## Third Semester B.E. Degree Examination, June / July 2014 **Analog Electronic Circuits**

Time: 3 hrs.

Max. Marks:100

Note: Answer FIVE full questions, selecting at least TWO questions from each part.

- 1 (ii) Reverse biased.

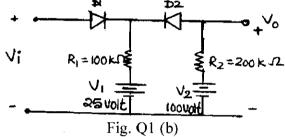

- In the circuit shown in Fig. Q1 (b) when the input varies linearly from 0 to 150 volts, sketch the output voltage to the time scale assuming the ideal diodes. (08 Marks)

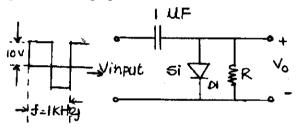

Explain the working of circuit shown in Fig. Q1 (c) and also sketch the output waveform. Also calculate the value of resistance R required to have a time constant equal to five times the product of RC during the discharge period. Given  $V_r = 0.7$  volt for Si diode.

Fig. Q1 (c)

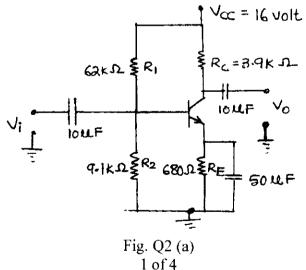

Find the quiescent collector current I<sub>C</sub> and voltage V<sub>CE</sub> for the circuit shown in Fig. Q2 (a) using exact analysis. Assume  $V_{BE} = 0.7$  volt and B = 80. (08 Marks)

- 2 b. Derive the expression for the stability factor  $S_{(ICO)}$ ,  $S_{(V_{BE})}$  and  $S_{(B)}$  for the fixed bias circuit. (06 Marks)

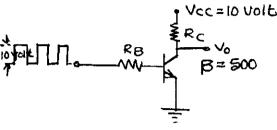

- c. Determine the value of  $R_B$  and  $R_C$  for the circuit shown in Fig. Q2 (c). Given  $V_{BE} = 0.7$  volt and  $I_{Csat} = 20$  mA. Select the base current  $I_B$ , 50% more to ensure saturation. (06 Marks)

Fig. Q2 (c)

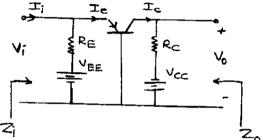

3 a. Find Zi, Zo, Av and A<sub>I</sub> for the common base circuit shown in Fig. Q3 (a) using approximate hybrid model. (10 Marks)

Fig. Q3 (a)

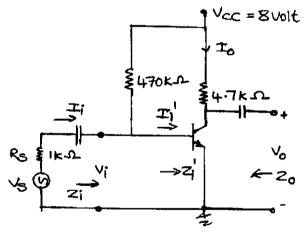

- b. For the network shown in Fig. Q3 (b) determine the following parameters using complete hybrid equivalent model:

- (i)  $Z_i$  and  $Z'_i$

- (ii) Voltage gain A<sub>V</sub>

- (iii) Current gain A<sub>1</sub> (iv) Z<sub>0</sub>.

Fig. Q3 (b)

Given

$$h_{fe} = 110$$

,  $h_{ie} = 1.6 \text{ K}\Omega$ ,  $h_{re} = 2 \times 10^{-4}$ ,  $h_{oe} = 20 \mu \text{A/volt}$

- 4 a. Describe the Miller effect capacitance and derive an equation for Miller input and output capacitances. (06 Marks)

- b. Three amplifiers with voltage gain 10, 100 and 1000 are connected in cascade. Find

- (i) The overall voltage gain in dB.

- (ii) The output voltage when the input voltage is 1  $\mu$ V.

(04 Marks)

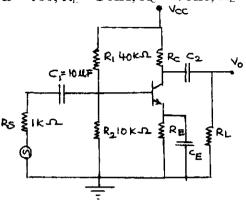

Determine the lower cut off frequency f<sub>LS</sub> for the network shown in Fig. Q4 (c). Given:  $V_{CC} = 20 \text{ V}$ ,  $r_0 = \infty$ , B = 100,  $R_E = 2 \text{ K}\Omega$ ,  $R_C = 4 \text{ K}\Omega$ ,  $R_L = 2.2 \text{ K}\Omega$ . (10 Marks)

Fig. Q4 (c) PART - B

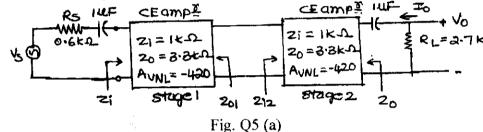

- For the two stage cascade amplifier shown in Fig. Q5 (a), determine 5

- (i) The loaded voltage gain of each stage.

- (ii) The total gain of the system  $A_V$  and  $A_{VS}$ .

- (iii) The loaded current gain at each stage.

(08 Marks)

- Draw the current series feedback circuit and derive an expression to find the output (06 Marks)

- What is negative feedback and write the advantages of negative feedback? (06 Marks) c.

- Explain the working of a series fed class A power amplifier and also derive an expression to (08 Marks) find the max efficiency of the amplifier.

- A class B push pull amplifier with  $V_{\text{CC}}$  = 25 volt driving a 8  $\Omega$  load find, b.

- (i) Maximum input power.

impedance.

- (ii) Maximum output power.

- (iii) Maximum circuit efficiency.

- (iv) Maximum collector dissipation.

(08 Marks)

What is cross over distortion and how it can be eliminated?

(04 Marks)

- What is an oscillator? Explain the Bark hausen criterion for sustained oscillations. (04 Marks)

- A quartz crystal has L = 3 Henry, C = 0.05 pf, R = 2 K $\Omega$  and C<sub>M</sub> = 10 pF. Find the series b. and parallel resonance frequency. (06 Marks)

- c. Draw the circuit diagram of a Weinbridge oscillator and write the expression to calculate (05 Marks) frequency of oscillation and loop gain.

- In a collpitts oscillator  $C_1 = 100 \text{ pF}$  and  $C_2 = 60 \text{ pF}$ , find the value of inductor L if the frequency of oscillation required is 50 KHz. (05 Marks)

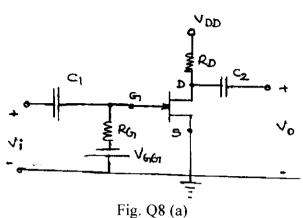

a. Draw the ac equivalent for the network shown in Fig. Q8 (a) using small signal ac model and find (i) Input impedence Z<sub>i</sub> (ii) Output impedence Z<sub>0</sub> (iii) Voltage gain A<sub>V</sub>.

(10 Marks)

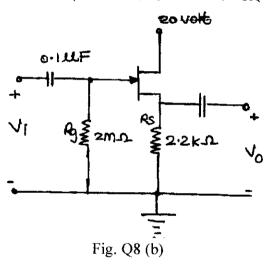

- b. For the JFET in common drain configuration shown in Fig. Q8 (b), calculate

- (i) The input impedance Z<sub>i</sub>.

- (ii) Output impedence Z<sub>0</sub>.

- (iii) Find  $V_0$  if  $V_i = 20$  m volt (p p)

(10 Marks)

Given:  $I_{DSS} = 10 \text{ mA}$ ,  $V_p = -5 \text{ volt}$ ,  $r_d = 40 \text{ K}\Omega$ ,  $V_{GSQ} = -2.85 \text{ volt}$

\* \* \* \* \*